### dentification of error sources Tinite ON resistance and leakage currents. Ty reduces component count and cost eal of these ICs are the DG506 to DG509 (Silice

# Reduce CMOS-multiplexer troubles through proper device selection

CMOS analog multiplexers exhibit problems with output leakage currents and overvoltage-protection circuitry. Here's how to deal with them.

#### Dick Wilenken, Intersil Inc

A CMOS analog multiplexer (MUX) is basically a channel-selector switch which can interface signal sensors and computers. It provides a number of input channels, which are time-shared onto a common output terminal. A central computer or microprocessor digitally sequences the MUX to "see" one channel at a time. The goal of designers is to pass the sensed signal through this multiplexer with virtually no error terms present. Providing adequate overvoltage protection also presents a challenge. Both objectives can tax designers' ingenuity unless they are familiar with multiplexer anatomy.

Many designers devise unnecessarily complex

circuits in their efforts to avoid the substantial level of error terms that can be encountered during the multiplexing operation and to provide overvoltage protection for the CMOS circuitry. But you can save pc-board space, reduce component count and cost, and avoid the possibility of introducing new errors through proper identification of error sources. And adequate circuit self-protection is the result of the proper choice of multiplexing devices.

#### Output leakage—the major error source

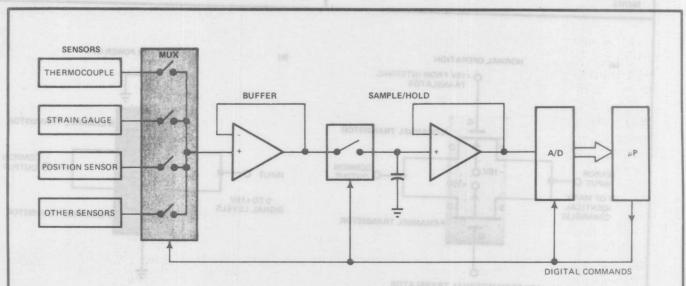

A typical data-acquisition system, extending from sensors to computer, is shown in Fig 1. Here the sensors feed directly into the multiplexer input lines, but this is an idealized case, because

Fig 1—Although the multiplexer diagrammed here is a 1-of-4 device, multiplexers in data-acquisition systems can switch as few as two or as many as 1000 channels to a common output.

### Identification of error sources reduces component count and cost

most users insert operational amplifiers between the sensors and the MUX inputs. You can eliminate these op amps, however, if you util1ze an IC MUX with very low output leakage currents.

SENSOR INPUT Vin O TOTAL TOTAL

Fig 2—With all but one channel OFF, this equivalent circuit for the MUX/buffer portion of Fig 1 shows potential error terms.

Most popular CMOS analog multiplexers have finite ON resistance and leakage currents. Typical of these ICs are the DG506 to DG509 (Siliconix), HI506 to HI509 (Harris) and the IH6116/6208 Series (Intersil).

As noted, the design goal for the system in Fig. 1 is to transfer the sensed signal into the sample-and-hold circuit with as little error as possible. Some potential error sources are labeled in Fig 2. One such error source arises from a voltage-divider action between r<sub>DS(ON)</sub> of a multiplexer ON channel (a consequence of finite channel resistance) and the input impedance of the follower op amp (Rin). The signal level at the positive input of the op amp is equal to the sensor voltage times R<sub>in</sub>/R<sub>in</sub>+r<sub>DS(ON)</sub>. And the error produced is equal to the ratio of Rin to Rin+rDS(ON) Because Rin (at low frequencies to dc level)=100M $\Omega$  and  $r_{DS(\Omega N)}=1~k\Omega$ , the error equals  $10^{8}/10^{8}+10^{3}=1/1+10^{-5}$ . This set of conditions yields an accuracy of 0.001%; r<sub>DS(ON)</sub> can range as high as 10 k $\Omega$  and still provide 0.01% accuracy. The obvious conclusion to be drawn is that the rosion

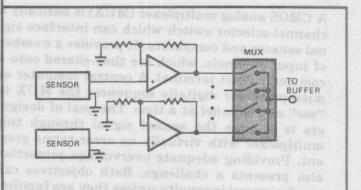

Fig 3—Boosting sensor output levels can overcome leakage and  $r_{\rm DS(ON)}$  errors, but you must pay for the added op amps and the resistors.

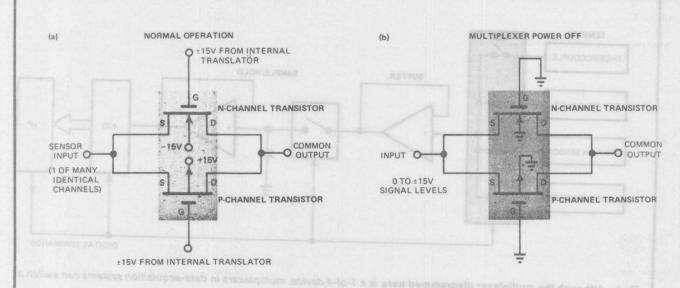

Fig 4—The diagram in (a) shows a typical CMOS MUX channel; (b) and (c) demonstrate the effects of power-down and overvoltage faults, respectively. Inserting diodes in the MUX supply lines affords protection from excessive currents (d).

of the ON channel is not a very significant factor so long as it is less than 10 k $\Omega$ .

A second and much more significant source of multiplexer error stems from ITOTAL (basically total leakage plus input bias current) flowing across r<sub>DS(ON)</sub>. (The total leakage is the sum of the OFF-channel leakage plus the I<sub>ON</sub> channel leakage.) For example, assume that I<sub>OFF(1-4)</sub>=150 nA,  $I_{ON}=25$  nA and  $r_{DS(ON)}=2$  k $\Omega$ , all at 125°C. The voltage drop across r<sub>DS(ON)</sub> is then 175 nA times 2  $k\Omega$ , or 350  $\mu V$ . This 350- $\mu V$  figure might be considered acceptable if the sensor output were 10V FS. However, thermocouple outputs of 16 mV FS over a 160°C temperature range correspond to 100 μV/°C. Thus, the 350-μV voltage drop across the switch is equivalent to a 3.5°C error—a deplorable level of accuracy. Of course, the same error would be reduced by a factor of approximately 1000 when the ambient temperature drops from 125°C to 25°C: 0.350 µV at 25°C is virtually error-free,

Specifically, the error factors cannot be reduced to  $r_{\rm DS(ON)}$  of the ON channel, but rather to ( $I_{\rm output\ leakage}+I_{\rm input\ leakage})r_{\rm DS(ON)}$ . The currently available DG506 (1-of-16) multiplexers are specified at 500 nA max at  $125^{\circ}\text{C}$ , and  $r_{\rm DS(ON)}$  is in the  $500\Omega$  range, producing an error term of  $250~\mu V$  for the multiplexer itself (exclusive of op-amp input bias currents). By comparison, IH6116 parts are rated at 100~nA max at  $125^{\circ}\text{C}$ , with  $r_{\rm DS(ON)}$  of  $1~\text{k}\Omega$ ; the maximum error term therefore equals  $100~\mu V$ , or  $\pm 1^{\circ}\text{C}$  for typical thermocouple sensors.

#### Dealing with leakage

Fig 3 is a block diagram of a circuit providing a solution to the problem of leakage and  $r_{\rm DS(ON)}$  errors. In it, the signal levels are boosted so that

the MUX error becomes a much smaller proportion of the multiplexer input signal. But this technique is expensive; the parts count is larger, more pc-board space is used, and new sources of error are introduced: op-amp offsets and temperature drifts.

You can zero the raw offset down to 100  $\mu V$  with a \$0.50 potentiometer. But how do you reduce offset drift?

Because the thermocouple scale is 100  $\mu V/^{\circ}C$ , the op-amp drift must be no greater than 100  $\mu V/^{\circ}C$  to contribute less than 10% error. Therefore, the best solution is to avoid inserting op amps between the sensors and the multiplexer, and to choose instead a multiplexer with significantly lower output leakages.

You might have to spend a few dollars more to obtain a MUX specified at, say, a maximum  $I_{\text{D(OFF)}} \leq 100 \text{ nA}$  at 125°C. But the alternative is the 16 op amps and all those gain resistors required for 16 channels of low-level sensing. And even if you use 741s, following this approach will cost you at least \$4 (16 op amps at \$0.25 each). However, if you choose a MUX with the lower leakage specifications, you'll save both money and pc-board space.

#### Overvoltage fault protection

As noted, CMOS multiplexers are designed to operate as sequential, time-shared multiple switches: When all supplies are correctly operating, only one channel is ON at a time. But when power supplies to a CMOS MUX are turned off, all sorts of damaging effects can occur.

Most of today's IC multiplexers operate from ±15V, GND and perhaps +5V. The sensor signals come from instruments powered by local sup-

### Channel ON resistance is not as significant as leakage currents

plies, which are usually independent of the MUX power supplies. When the multiplexer power is down while the signal inputs are active, the majority of today's CMOS multiplexers will not operate sequentially—instead, all channels will be turned ON simultaneously. In that case, one transducer is forced to drive the other transducers via the ON-channel resistances—operation that can be very tough on the sensors. The origin of this problem lies in the design and fabrication techniques currently employed in manufacturing a CMOS multiplexer like the DG506 or IH6116.

A typical CMOS channel circuit is shown in Fig 4a. If the sensor input signals are lower than ±15V with MUX power on, no malfunctions occur. But if the sensor signals exceed the levels of the MUX power supplies, or if the multiplexer power is off, the channels are coupled.

Fig 4b depicts a condition where the MUX power is down with sensor signals present. Note that with the power off, the gates and bodies of the parallel n- and p-channel MOSFETs are at ground potential. Because most threshold voltages fall in the range of 1 to 5V, the devices are in the enhancement mode (turned ON) when the signal levels exceed these threshold voltages.

For example, assume that  $\pm 5V$  levels are being switched, with the n-channel  $V_{threshold}$  at +2V and the p-channel  $V_{threshold}$  at -3V. Thus, for -5V levels, the  $V_{GS}$  of the n-channel device equals +5V when the gate is at ground potential; this value is +3V more than the threshold voltage, and the FET turns ON. A similar condition occurs at +5V levels, when as a result, the p-channel device is

turned ON. Either situation couples all channels with voltage levels higher than the MOSFET's threshold voltage.

While this coupling phenomenon occurs only with multiplexer power down, a similar situation occurs if the MUX power is at a normal  $\pm 15$ V level and the signal levels exceed  $\pm 15$ V, as happens with voltage spikes. Electrically, this condition is indistinguishable from the previous fault situation. Fig 4c shows that for levels in excess of -20V, the n-channel device's V<sub>GS</sub> equals -15V minus the -20V value (resulting in a final figure of +5V), and the device is enhanced (ON). The opposite condition occurs at +20V, when the p-channel device is ON. In either case, all channels are coupled.

Another harmful condition can occur either when a multiplexer is powered-down or when excessive signal levels are present: Heavy current supplied by the sensors flows into the bodies of the n-channel or p-channel MOSFETs; this current could damage the sensors.

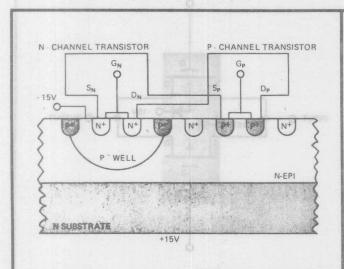

The origin of this problem lies in the junctionisolation technique inherent in the fabrication of CMOS devices. Fig 5 shows a cross-section of typical CMOS parts. Note that the body of the n-channel device contains the p- well (usually tied to -15V) and that the source-to-body junction is an n+/p – silicon junction that looks like a reverse-biased diode under no-fault operation. Specifically, the n+ source is  $\leq +15V$  and  $\geq -15V$ when the p- well is tied to -15V. When the -15V level is off, the p- well rides at ground potential, and the source might be forward-biased into the body. The only limits on current flow are the maximum current that the sensor can deliver and the bulk resistance of the substrate. A similar situation occurs in the p-channel device, at the source/body pn junction.

A common technique to prevent this excessive

Fig 5—Power-down or overvoltage faults forward-bias the n-channel source/p- well junction and the p-channel source/n-epi junction.

Fig 6—A series structure protects against power-down and overvoltage faults.

current flow from the sensor into the MOSFETs' bodies is to add diodes to the multiplexer supply lines, as shown in Fig 4d. Addition of these diodes reduces the signal-handling level to +14V (with  $\pm15V$  supplies). But this factor is somewhat academic because most operational amplifiers have maximum input levels below  $\pm14V$  (see the follower op amp in Figs 1 or 2).

#### Better protection with a new structure

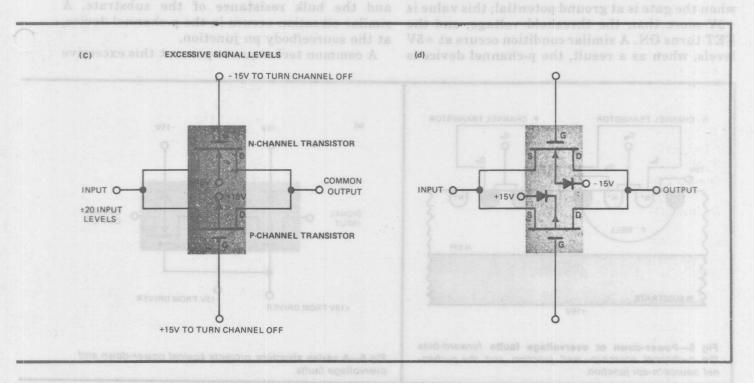

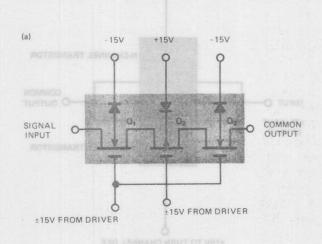

Another family of CMOS multiplexers (Intersil's IH5108 and IH5208), slated for introduction early this year, features an improved fault-protection structure. These devices have a series combination of n- and p-channel MOSFETs instead of the parallel arrangement found in more conventional devices.

The new structures' output-channel configuration is shown in Fig 6a. The series-connected n-channel devices are located on either side of the p-channel MOSFET. The IH5108/5208 IC's

OVERVOLTAGE WITH MUX POWER OFF (b) +25V FORCED  $\Omega_3$ OVERVOLTAGE ON COMMON o cathode OUTPUT EXTERNAL CIRCUITRY \* D N-CHANNEL MOSEET N-CHANNEL TURNED ON BECAUSE Vgs = +25V MOSFET IS OFF P-CHANNEL MOSFET IS OFF (c) OVERVOLTAGE WITH MUX POWER ON -15V +15V - 15V 0 0 25V +25V FORCED OVERVOLTAGE Q, ON COMMON 0. OUTPUT LINE BY EXTERNAL CIRCUITRY N-CHANNEL MOSFET N-CHANNEL S TURNED ON BECAUSE Vgs= MOSFET IS OFF +15V FROM DRIVERS 15V FROM DRIVERS P-CHANNEL MOSFET IS OFF

series-oriented design produces the following electrical characteristics:

- When the ±15V multiplexer power is off, all channels are OFF, rather than being ON as occurs in the parallel output stage in Fig 4.

- No current is drawn from the sensors—only leakage current is present.

- All channels remain OFF and draw only leakage currents for ±25V overvoltage inputs, regardless of whether multiplexer power is on or off.

Figs 6b and 6c show two fault conditions and the performance of the series multiplexers' structure under these conditions. In Fig 6b,  $Q_1$  is turned ON by the fault condition, but  $Q_2$  and  $Q_3$  remain OFF.  $Q_2$  and  $Q_3$  share a 50V breakdown, and the device with the lowest leakage has the highest voltage drop across it. The series structure is symmetrical, with an n-channel device on either side of the p-channel MOSFET. Reversing the 25V polarity has no effect, because only one n-channel device will be ON with either polarity in effect; the remaining two devices will always be OFF.

The same conditions exist in Fig 6c, with the  $\pm 15 \text{V}$  MUX power turned on. In this case, the gates are driven to -15 V for the n-channel devices and to +15 V for the p-channel transistor—corresponding to the OFF-channel condition. The gate drive voltages derive from the on-chip TTL translator circuitry. Again, as in Fig 6b,  $Q_1$  is turned ON by the overvoltage;  $Q_2$  and  $Q_3$  are OFF and serve to stand-off the 50V voltage drop.

# INTERSIL

### 74 8 8

# THIS IS THE FIRST ISSUE OF THE NEW INTERSIL INSIGHT.

We think you'll find it's the last word in what's new and important in linear integrated circuits, memory and microprocessor systems, data acquisition systems, power MOS devices, display drivers and more. Whenever you see an item that catches your interest, just check the appropriate number on the coupon on the back page for more product data. We call it the You Got Me! coupon. Be sure to check it, clip it, and send it in. Because at Intersil, we have answers.

### CMOS EPROM Programmer Operates Stand Alone or with Terminal.

Our microprocessor-controlled Model 6920 CMOS EPROM programmer is designed for use with the IM87C48/C41 single chip microcomputers and IM6653 (1K x 4) and IM6654 (512 x 8) CMOS EPROMs. And there are provisions for up to three additional types of CMOS EPROMs provided in the hardware. The 6920 operates with a terminal, as a stand-alone unit, or as a peripheral to a computer. It features built-in RS232C and 20mA current loop interfaces. And 14 different baud rates from 50 to 9600 can be selected. Check 02 for more on the 6920.

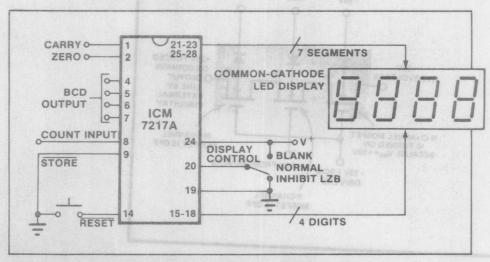

Monolithic

4-Digit Up/

Down

Counter

Directly

Drives LEDs

Up to 1" High.

The ICM7217/27 family of 4-digit up/ down counters will directly drive large multiplexed 7-segment LED displays. Either common anode or common cathode. The common anode devices typically drive 200mA per digit, 40mA per segment peak for bright displays. Or, go common cathode and use a calculator type display for lower power and display costs. Either way, forget external drivers or resistors. Features include: Presettable up/down counter and register. BCD inputs/outputs that drive TTL directly. Leading zero and display blanking. Low power standby mode - 300 µA typical with display off. Cascadable: 8 or more digits in blocks of four. Counting speed guaranteed to 2MHz. Single ±5V 10% supply. Check 03.

ere's a new high-performance equivalent to the classic 555 RC timer. The ICM7555 general purpose timer features a typical power supply current rating of only 80 μA. That's less than 1/20th required by its bipolar counterpart. We guarantee an expanded high speed operation to 500KHz. That's a five times improvement over the industry standard 555! The new Intersil units last longer, use less current and have a widened supply voltage range of 2 to 18V. 'eal for applications impossible with the old 4.5V bipolar 555's. Check 04 on the You Got Me! coupon.

Designed for Designers. 5 \( \mathbb{V} \text{V}\_{OS} \) Instrumentation Amplifiers.

A monolithic instrumentation amplifier with a unique commutating auto-zero design circuit principle. The ICL7605. While one op amp is in a signal processing mode, a companion device is switched into an error-null

configuration. The result: lower cost and better performance. With near-zero offset voltage temperature drift of only  $0.05~\mu\text{V/}^{\circ}\text{C}$ . Long-term input offset drift of  $0.2~\mu\text{V/}\text{year}$ . Open loop gain of greater than 105dB. 5pA input leakage current. And common mode rejection ratio (CMRR) of 110dB. CMOS construction fits low power requirements. It's the best low drift instrument amplifier that you can buy. And it only costs \$15 in lots of 100. Check number 05 on our *You Got Me!* coupon.

12-BIT A/D

CONVERTER:

\$10.

ere's the first ±12-bit monolithic A/D converter chip targeted for a wide variety of microprocessor applications, with a \$10 price tag in 100 unit quantities. The CMOS ICL7109 features a three-state output that can be directly interfaced to the data buses of microprocessors such as the Intersil 6100 or IM87C48, the Motorola MC6800 and the Intel 8080 and 8048. And it can be used for remote serial data logging applications. Just check 06 on the You Got Me! coupon for more info.

ID(ON) X RDS(ON) = Error

### Lowest Error MUX's.

New Intersil IH6116/IH6108 multiplexers are pin-for-pin replacements for the industry standard 16 and 8 channel MUX's you're probably using now. But, they offer the low power, low error performance of Intersil's latch-up proof CMOS process. They draw a maximum supply current of 0.2mA. And they consume only about 1/10 the power of their nearest competitor: 4.5mW Max., at ±15V. That means virtually no self-heating...leakage current of 0.2 n A @ 25° doesn't change as the device "warms up." You get the lowest power consumption and lowest leakage in the business. Just check 07 on the coupon.

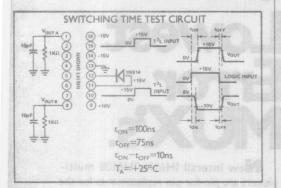

### HIGHEST SPEED, LOWEST POWER ANALOG SWITCHES ON THE MARKET.

t<sub>ON</sub>80ns typical and t<sub>OFF</sub>50ns typically characterize the ultra-fast switching times of the IH5140/IH5145. In fact, they're the fastest switches available! (They toggle at better than 1MHz.) And they combine the speed of the hybrid DG180 family with the inherent reliability and low power consumption of CMOS construction. The new switches are available in single or dual SPST, SPDT, or DPDT functions and feature power supply

currents of less than  $10\mu A$  Max. Check 08. And be sure to check into our entire family of analog switches. From monolithics to hybrids, Intersil has the answers.

# POWER MOS.

You get more efficient operation and fully characterized maximum ratings in our new IVN5200 family of VMOS power FETs: 80V BV<sub>DSS.</sub> 5A  $I_{D(ON)}$ .  $0.5\Omega R_{DS(ON)}$  Max. Ideal for high frequency switching power supplies, servo amplifiers, motor controls, high level analog switches...you name it. And the IVN5000 series of  $2.5\Omega$  to  $4.0\Omega$  devices. IVN5000 specs: 80V BV<sub>DSS.</sub>  $2.5\Omega R_{DS(ON)}$  Max. Choice of packages including TO-52 and TO-237. Great in applications such as peripheral interfaces and RF amplifiers. Plus, an alternate source for the Siliconix VN series. Check 09.

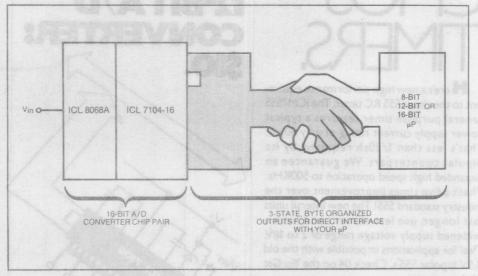

# A CMOS 16-BIT IC A/D CONVERTER: \$29.

First again! A true 16-bit A/D converter in IC form. It's called the ICL7104/8068 chip pair, and it's specifically intended for microprocessors. Its interface capability allows it to be used with virtually all microprocessor systems with buses up to 18 bits wide. And the high performance, low noise A/D chip set will operate in either close-in parallel or

handshake modes. There's more. 16-bit binary resolution is 1 part in 65,536. Maximum non-linearity is 1 count over  $\pm$  full scale. Resolution (10  $\mu$ V per count. Voltage noise  $\approx 2 \mu$ V. True auto zero. Zero drift 0.5  $\mu$ V/°C. Full-scale Tempco 2ppm/°C (ext. ref.). Ratiometric operation. Direct interface to any  $\mu$ P or UART. Check 10.

## LOWEST VOLTAGE IN THE INDUSTRY WITH CMOS OP AMP FAMILY.

where ultra-low input current and minimum power consumption are essential parameters. The new ICL7611 family of CMOS Op Amps. Low voltage operation is guaranteed at  $\pm$  0.5V (the lowest in the industry) to  $\pm$ 8.0V, while providing output swings to within a few millivolts of the supply voltage rails. And they're capable of single-ended operation from a single NiCd battery. A novel quiescent current selection pin allows the user to program currents of 1mA,  $100\,\mu\text{A}$  or  $10\,\mu\text{A}$ , without external

components. That means a power drain as low as 10  $\mu$ W. Input currents of 1pA are 30 times lower than those of BiFETs. And the other parameters are just as impressive. The ICL7611 family devices are available as singles, duals, triples, and quads in internally-compensated or uncompensated configurations. For the rest of the specs on the lowest voltage op amps in the industry, check 11.